First Blog Post, and I made some progress on research...

07-July-2020

I finally got RCV back in a relatively working order. So far I have been testing it on a custom FPGA architecture file with greatly exaggerated hold time requirements on internal flipflops, to encourage hold time violations during routing.

Ideally the algorithm I'm implementing would encourage the wiring to take longer paths, if it thinks there would be a hold, or short path violation, thus increasing the delay in a connection and potentially resolving these issues.

Having tested the algorithm on smaller circuits, it's shown to completely remove short path violations, while still meeting the frequency constraints set by an engineer to a certain degree.

It is having trouble with larger circuits, that require more routing, and it takes significantly longer than without the algorithm, but these are all next steps!

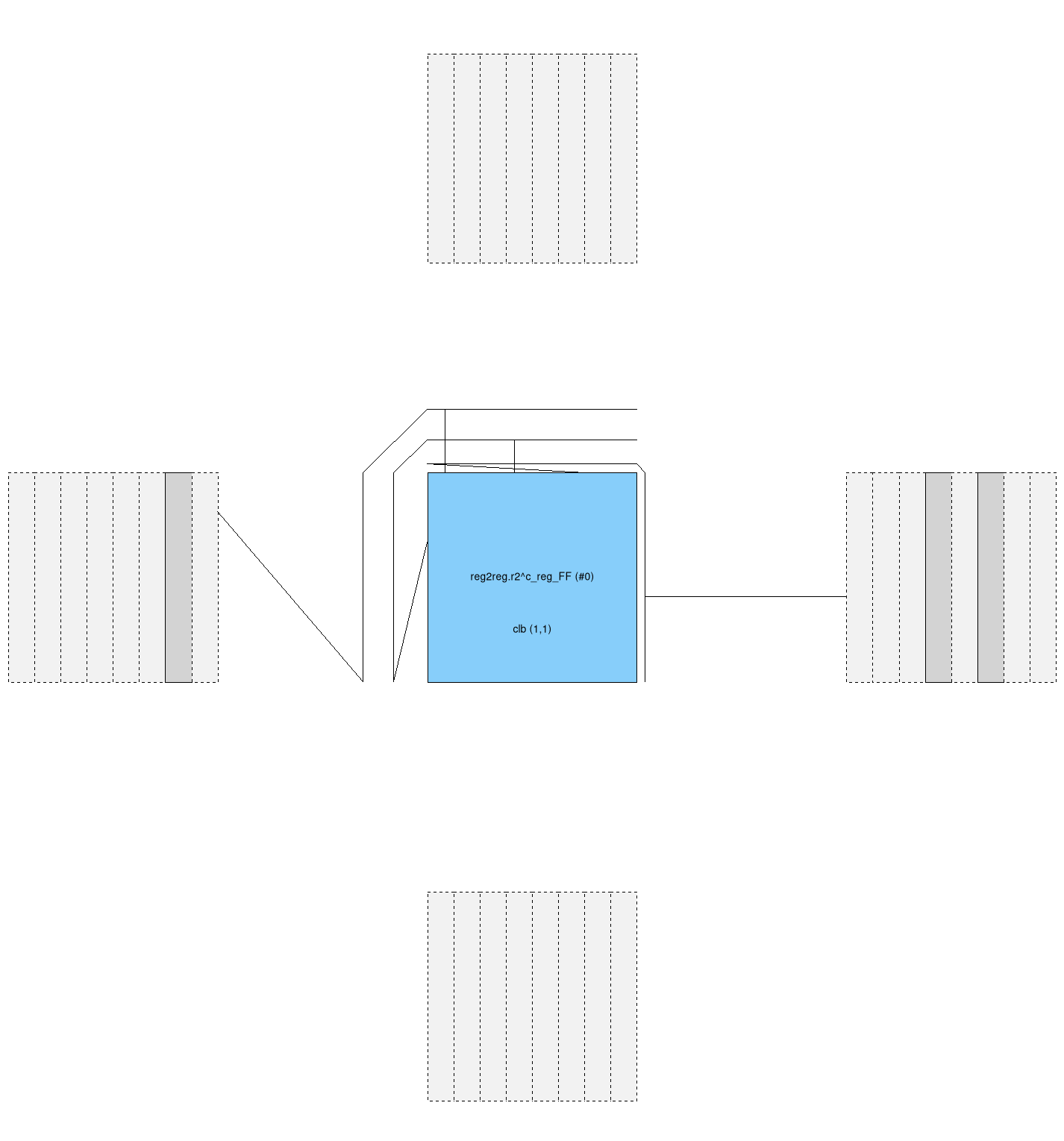

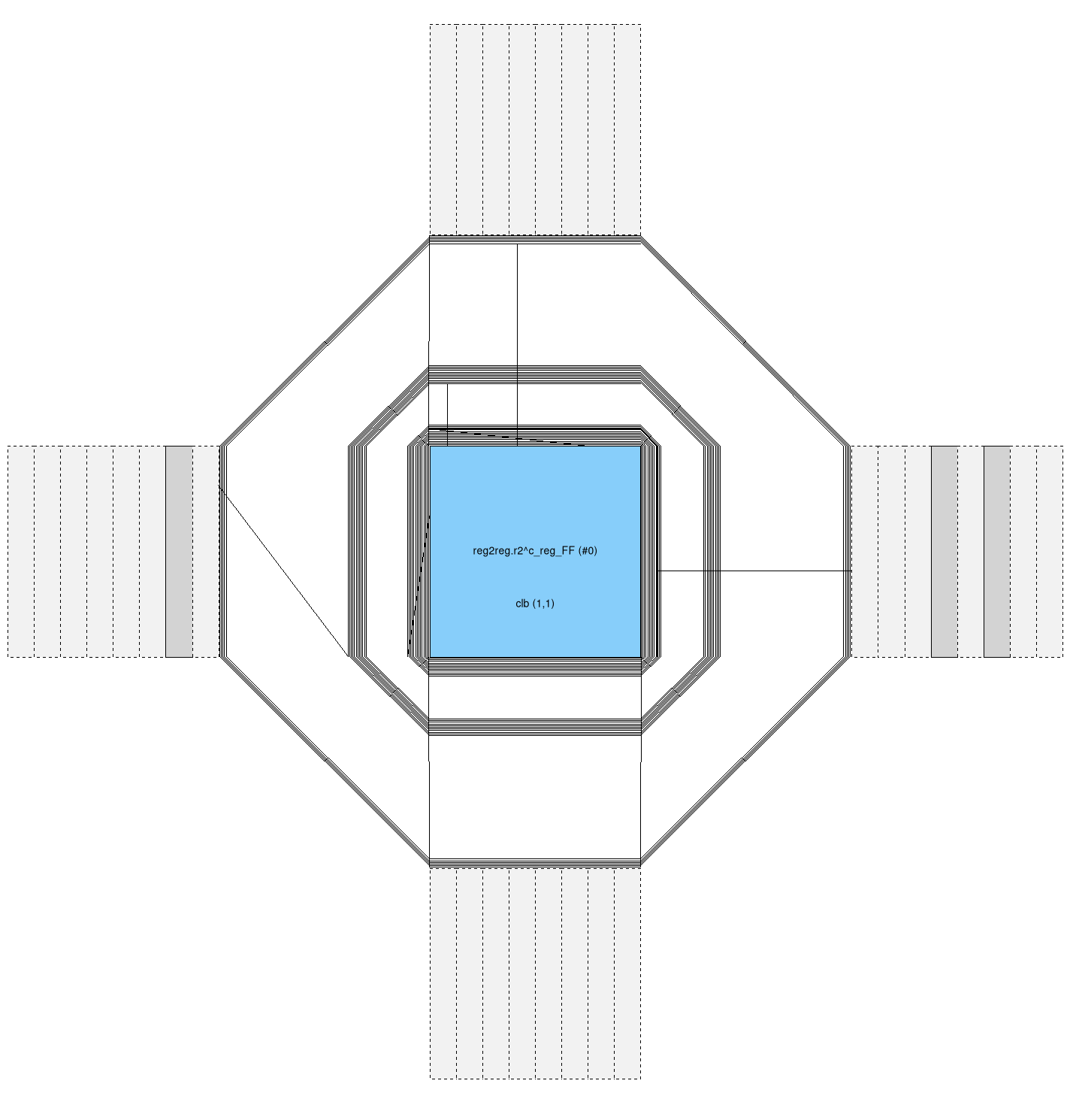

The pictures on the right represent the effect my algorithm has on one of the simplest circuits, a single register to another register, also running on another modified architecture with the same hold time requirements, with no clustering.

As can be seen, before running my algorithm, the router simply chooses the fastest routing it can find, and then discovers that the route it has taken is too fast. The end results is the router lapping the LUT in an effort to increase connection delay, a result I find beautiful.

As expected, it does resolve these timing issues.

Ideally the algorithm I'm implementing would encourage the wiring to take longer paths, if it thinks there would be a hold, or short path violation, thus increasing the delay in a connection and potentially resolving these issues.

Having tested the algorithm on smaller circuits, it's shown to completely remove short path violations, while still meeting the frequency constraints set by an engineer to a certain degree.

It is having trouble with larger circuits, that require more routing, and it takes significantly longer than without the algorithm, but these are all next steps!

The pictures on the right represent the effect my algorithm has on one of the simplest circuits, a single register to another register, also running on another modified architecture with the same hold time requirements, with no clustering.

As can be seen, before running my algorithm, the router simply chooses the fastest routing it can find, and then discovers that the route it has taken is too fast. The end results is the router lapping the LUT in an effort to increase connection delay, a result I find beautiful.

As expected, it does resolve these timing issues.

Before fixing hold violations

After fixing hold violations